NAMA :

BRIAN RIAN REHAN

KELAS :

2IA12

NPM :

50420296

Soal!

Jelaskan secara rinci apa yang dimaksud dengan :

1. Half adder

2. Full Adder

3. Half Subtractor

4. Full Subtractor

Jawaban

Half Adder

Sirkuit logika yang digunakan

untuk menambahkan dua angka 1-bit atau hanya dua bit disebut sebagai sirkuit

Half Adder. Sirkuit ini memiliki dua input dan dua output. Input adalah dua

bilangan biner 1-bit (dikenal sebagai Augend dan Addend) dan outputnya adalah

Sum and Carry. Gambar berikut menunjukkan diagram blok Half Adder. Tabel

kebenaran dari Half Adder ditampilkan dalam tabel berikut.

Jika kita mengamati nilai'Sum'

dalam tabel kebenaran di atas, itu menyerupai Gerbang Ex-OR. Demikian

pula, nilai-nilai untuk 'Carry' dalam tabel kebenaran di atas menyerupai

Gerbang AND.

Jadi, untuk menerapkan Half Adder

dengan benar, Anda memerlukan dua Logic Gates: gerbang XOR untuk Output 'Sum'

dan gerbang AND untuk output 'Carry'. Gambar berikut menunjukkan Diagram

Logika Dari Half Adder.

Di sirkuit setengah adder di

atas, input diberi label sebagai A dan B. Output 'Sum' diberi label

sebagai simbol penjumlahan (∑) dan output Carry diberi label dengan CO.

Half adder terutama digunakan

untuk penambahan augend dan addend dari angka biner orde pertama yaitu, angka

biner 1-bit. Kami tidak dapat menambahkan angka biner dengan lebih dari

satu bit karena Half Adder tidak dapat menyertakan informasi 'Carry' dari jumlah

sebelumnya.

Karena keterbatasan ini, Half

Adder praktis tidak digunakan dalam banyak aplikasi, terutama dalam penambahan

multi-digit. Dalam aplikasi seperti itu, carry penambahan digit sebelumnya

harus ditambahkan bersama dengan dua bit; oleh karena itu adalah tambahan

tiga bit.

Full Adder

Full Adder adalah sirkuit logika

kombinasi yang melakukan penambahan pada tiga bit dan menghasilkan dua output:

Sum dan Carry. Seperti yang telah kita lihat bahwa Half Adder tidak dapat

menanggapi tiga input dan karenanya adder penuh digunakan untuk menambahkan

tiga digit sekaligus.

Ini terdiri dari tiga input, dua

di antaranya adalah variabel input yang mewakili dua bit signifikan yang akan

ditambahkan, sedangkan terminal input ketiga adalah carry dari penambahan

sebelumnya. Dua output adalah output Sum dan Carry.

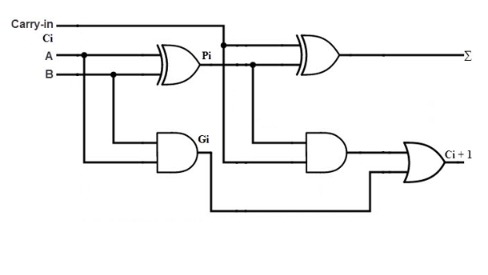

Gambar berikut menunjukkan

diagram blok dari Full Adder di mana input diberi label sebagai A, B dan CIN,

sedangkan output diberi label sebagai ∑ dan COUT.

Datang ke tabel kebenaran, tabel

berikut menunjukkan tabel kebenaran dari Adder Penuh.

Dari tabel kebenaran di atas,

kita bisa mendapatkan Ekspresi Boolean untuk Output Sum dan Carry. Dengan

menggunakan ekspresi tersebut, kita dapat membangun sirkuit logika untuk Full

Adder. Tetapi dengan menyederhanakan persamaan lebih lanjut, kita dapat

memperoleh pada titik bahwa Full Adder dapat dengan mudah diimplementasikan

menggunakan dua Half Adders dan OR Gate.

Gambar berikut menunjukkan

Sirkuit Adder Penuh yang diimplementasikan menggunakan dua Half Adders dan

GERBANG OR. Di sini, A dan B adalah bit input utama, CIN adalah input

carry, ∑ dan COUT adalah Sum dan Carry Outputs masing-masing.

Half Subtractors

Half Subtractor adalah Multiple

Output Combinational Logic Circuit yang melakukan pengurangan dua bilangan

biner 1-bit. Ini memiliki dua input dan dua output. Kedua input

sesuai dengan dua angka biner 1-bit dan dua output sesuai dengan bit Difference

dan Borrow bit (berbeda dengan Sum and Carry in Half Adder).

Tabel berikut menunjukkan tabel

kebenaran dari Half Subtractor.

Dari tabel kebenaran di atas,

kita dapat mengatakan bahwa output 'Perbedaan' dari Half Subtractor mirip

dengan output XOR (yang juga sama dengan output Sum dari Half

Adder). Dengan demikian, Half Subtraction juga dilakukan oleh gerbang

Ex-OR dengan gerbang AND dengan satu input terbalik dan satu input normal, yang

diperlukan untuk melakukan operasi Pinjam.

Gambar berikut menunjukkan

sirkuit logika Half Adder.

Sirkuit ini mirip dengan Half

Adder dengan hanya perbedaan menjadi input minuend yaitu, A dilengkapi sebelum

diterapkan di gerbang AND untuk mengimplementasikan output pinjaman.

Dalam kasus pengurangan

multi-digit, pengurangan antara dua digit harus dilakukan bersama dengan meminjam

pengurangan digit sebelumnya, dan karenanya subduksi harus memiliki tiga input,

yang tidak mungkin dengan Half Subtractor. Oleh karena itu, setengah

pengurangan memiliki serangkaian aplikasi terbatas dan sebenarnya, itu tidak

digunakan dalam praktik.

Full Subtractor

Full Subtractor adalah rangkaian

logika kombinasional yang melakukan pengurangan antara dua bilangan biner 1-bit

dan juga mempertimbangkan pinjaman dari bit sebelumnya yaitu, apakah 1 telah

dipinjam oleh bit minuend sebelumnya.

Jadi, Full Subtractor memiliki

tiga input, di mana dua input yang sesuai dengan dua bit yang akan dikurangi

(minuend A dan subtrahend B), dan sedikit pinjaman, biasanya direpresentasikan

sebagai BIN, sesuai dengan operasi pinjam. Ada dua output, satu sesuai dengan

perbedaan output D dan yang lainnya Pinjam output BO.

Gambar berikut menunjukkan

diagram blok dari pengurangan penuh.

Tabel berikut menunjukkan tabel

kebenaran dari Pengurangan Penuh.

Dengan menurunkan ekspresi

Boolean untuk sub kurangi penuh dari tabel kebenaran di atas, kita mendapatkan

ekspresi yang mengatakan bahwa pengurangan penuh dapat diimplementasikan dengan

setengah pengurangan dengan gerbang OR seperti yang ditunjukkan pada gambar di

bawah ini.

Dengan membandingkan sirkuit adder dan subtractor dan tabel kebenaran, kita

dapat mengamati bahwa output D dalam pengurangan penuh persis sama dengan

output S dari adder penuh. Dan satu-satunya perbedaan adalah bahwa

variabel input A dilengkapi dengan pengurangan penuh.

Oleh karena itu, dimungkinkan untuk mengubah sirkuit adder penuh menjadi pengurangan penuh hanya dengan melengkapi input A sebelum diterapkan ke gerbang untuk menghasilkan output bit pinjaman akhir Bo.